設計時における電源プレーンの共振解析

基板の銅箔は上下に隣接していると共振というものが発生します。

つまり並行平板のパッチアンテナとして機能してしまうということです。また、銅箔で形成されたプレーンの大きさや形によって、共振する周波数は様々で、例えば電源の小さなリップルノイズの周波数が共振するとノイズが増幅されて空間に放射されてしまうことから、それらを抑えなければならないというわけです。

プレーン共振解析も基板を作る前の設計段階で対策するものです。

弊社はNEC様のDEMITASNXというプロダクトを運用し、ノイズ抑制支援ツールとして活用しています。

プレーン共振解析とはどんなことをやっているのか、簡単なしくみを3つ説明します。

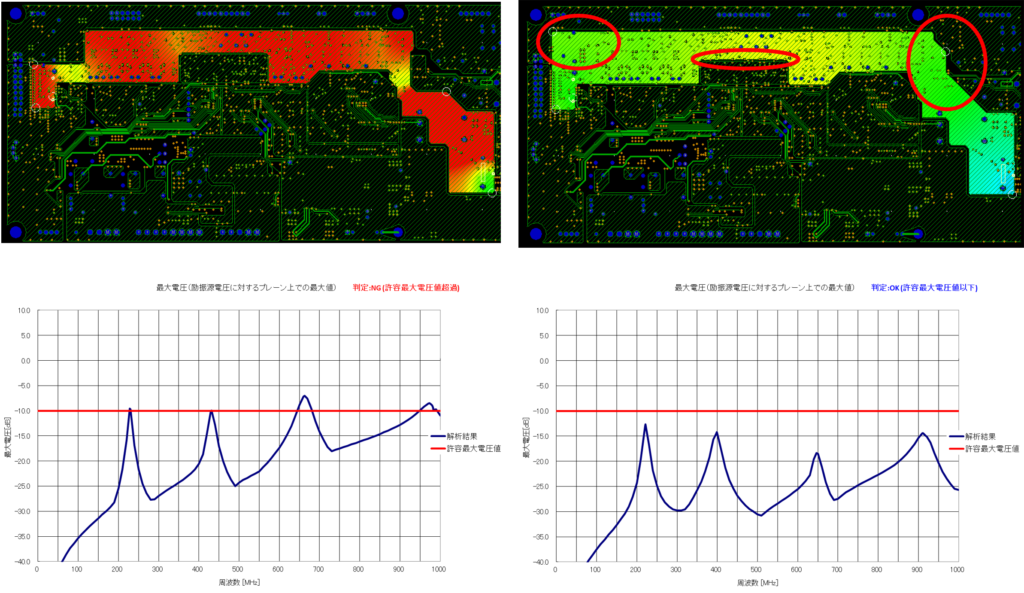

1.プレーン形状変更

プレーンの形状を変える。細長いプレーンや無駄に面積が大きいと共振しやすい。これが一番コストがかからない。でも難しい。どうすれば改善させることができるかあまり良く分かっていない基板設計者が多い。特に電源種が多い基板になると分割することに注力され、形状など気にしていられないのが実態。

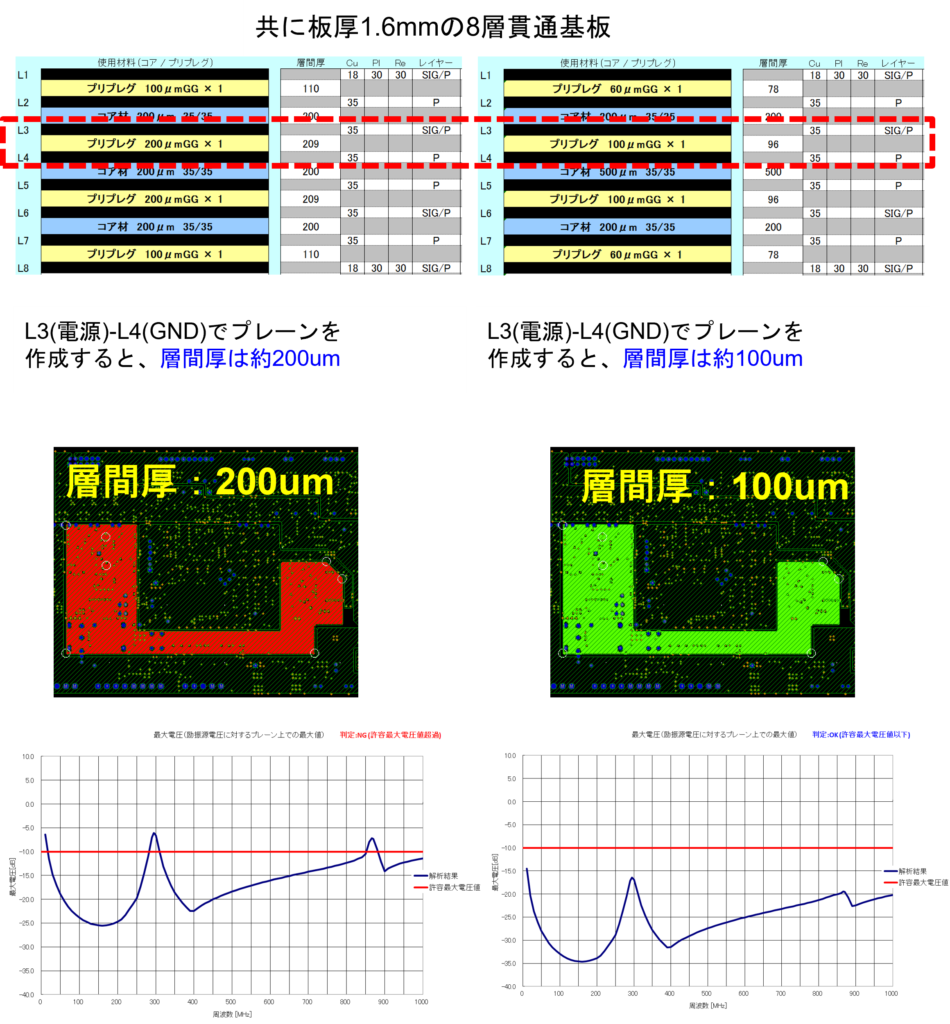

2.層構成プランニング

次の対策手法は層構成で基板そのものの共振を抑えるアプローチです。

具体的には電源プレーンとGNDプレーンの層間を薄くさせると共振が低減される例です。

電源プレーンの形は全く同じものでも層間を薄くするだけで共振の電圧レベルが下がります。これは、電源プレーンのインピーダンスが全体的に下がることにより、共振の電圧レベルも下がるからです。

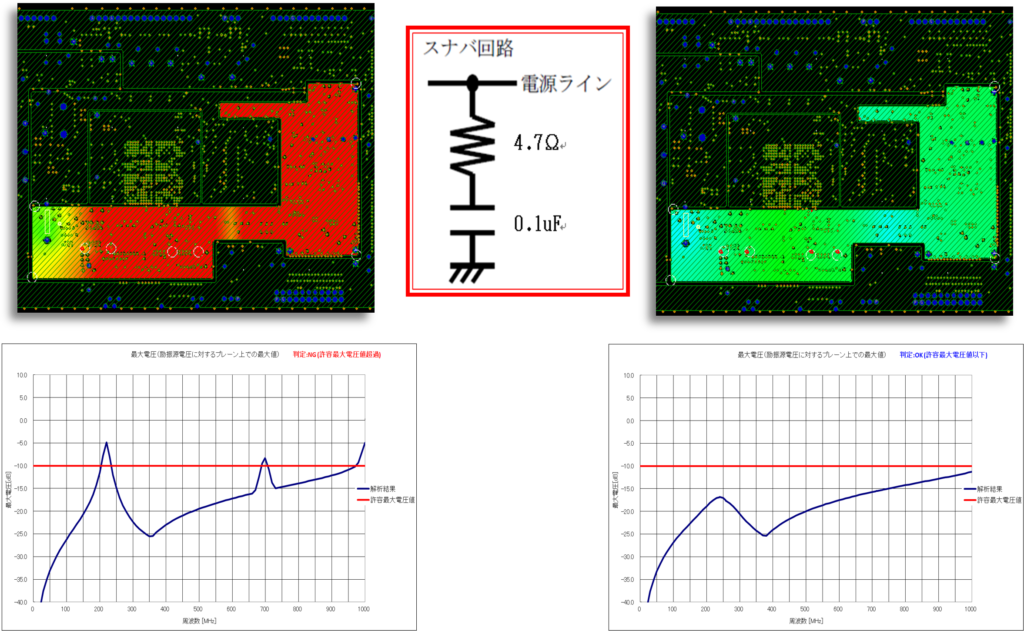

3.部品の追加

次に、キャパシタやRCスナバ回路を追加する例です。これが一番手っ取り早い対策手法かもしれません。次の絵が対策を施した後になりますが、4.7Ωと0.1uFを直列につないだ部品を、共振が著しい場所に置いた結果となります。

抵抗とキャパシタそれぞれの値は実装学会で提示されたものを参考にさせて頂いております。

ただ、この様な受動部品自体は安価ではありますが、それに紐付く実装費用や管理費などが上乗せされるため、無暗に追加したくないという意見が本音かもしれません。よってこの対策は最終手段と位置付けております。

プレーン共振解析のメリット

多層基板では、電源プレーンは内層に有る事がほとんどです。その為、基板製造後には対策を行うことが難しくなります。事前に確認しておくことで試作回数の削減、またはよりノイズ耐性のある製品開発につながります。もちろん、試作回数が減れば大きな費用削減につながります。