12G-SDIのリターンロス特性

12G-SDIはSMPTE ST 2082にて規格が確立されており、その中のうちの一つにリターンロス特性の要求値があります。

リターンロスとは反射損失のことで、伝送する進行波と反射波の比をデシベルで表現し、12G-SDIは周波数帯域毎にスペックが規定されています。また、値がが小さいほど信号を悪化させる要素が少ないとも言えます。

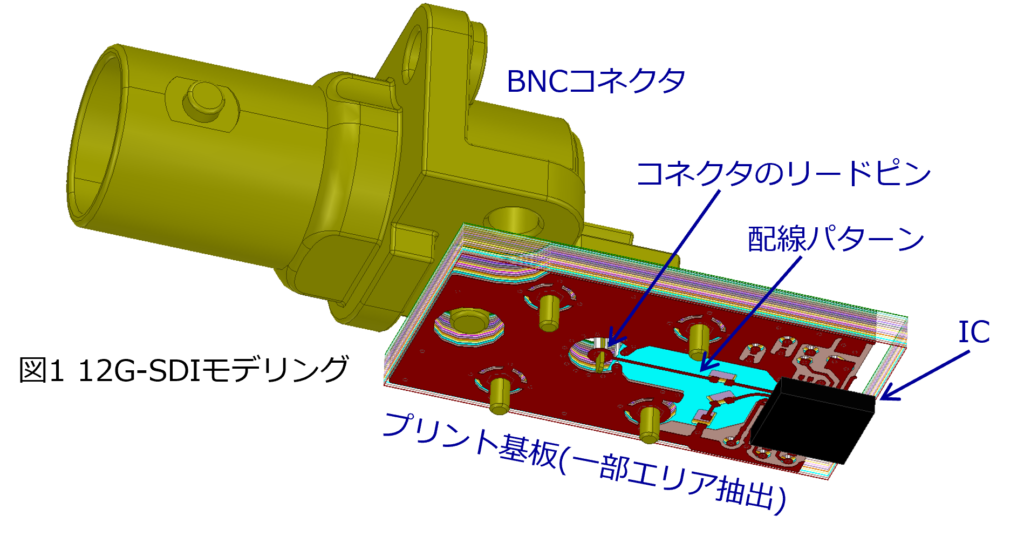

図1はBNCコネクタ、プリント基板、ICをモデリングした概念図です。

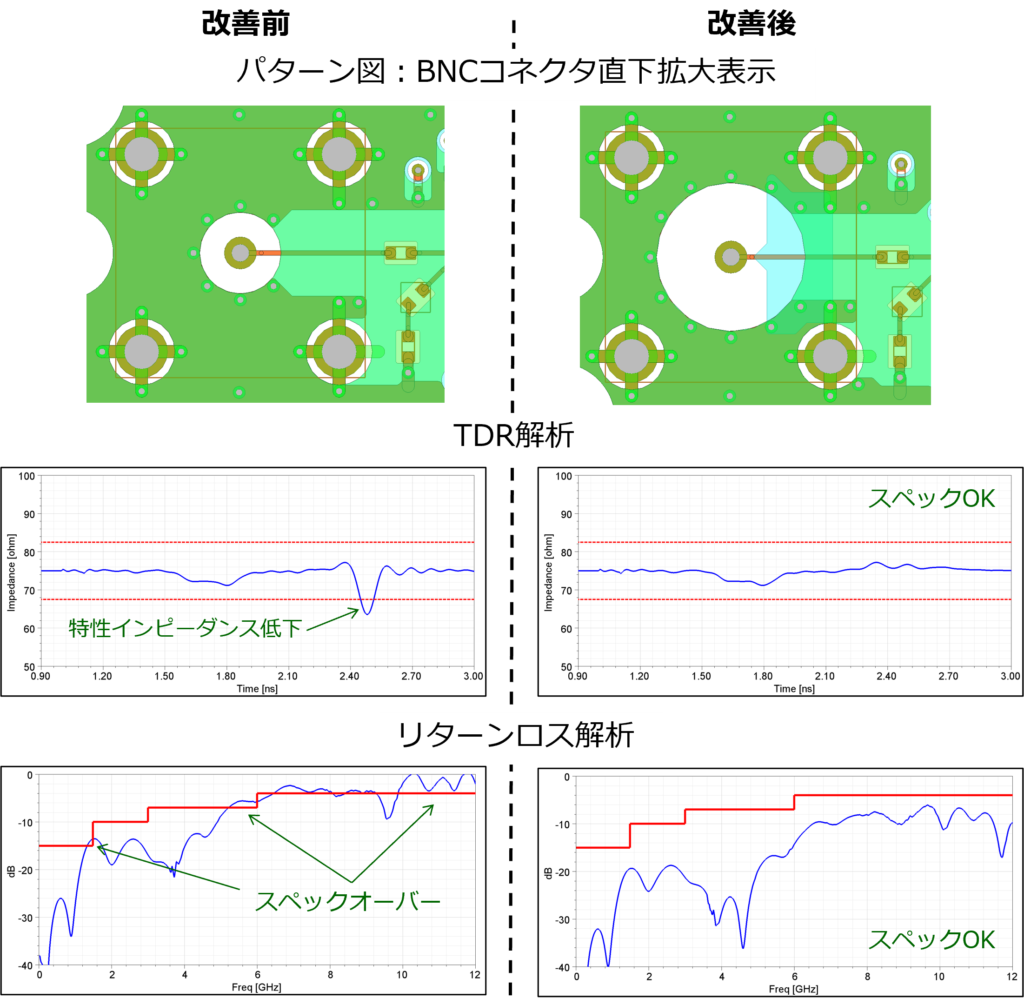

基板設計時にシミュレーションを実施し最適化を行わないと、実機測定においてリターンロス規格を満足しない場面に遭遇します。伝送線路の特性インピーダンスは75Ωですが、配線パターン以外の要素、例えばスルーホール部分でインピーダンス不整合が起こったり、コネクタのリード径や層構成などは様々であるため、一様に設計することはできません。

基板設計段階でTDR解析、リターンロス解析をシミュレーションすることで部品レイアウトや配線パターンの問題箇所を把握しつつ修正を施すことが可能です。

BNCコネクタやIC (Cable Driver, Equalizer)の特性を加味(Sパラメータ)することで、より実機に近いモデリングとなり、解析精度の向上が期待できます。

1.ICの搭載面をBNCコネクタとは反対の面となるように設置します。

同一面に搭載すると配線パターンに対しリードピンがオープンスタブとなり反射を招きますので、それらを防止するためです。

2.リードピンのスルーホール部分が75Ωとなるように調整します。

スルーホールにはランドがあるだけでなく穴の内壁にメッキが付くことで容量成分が高まり、特性インピーダンスが75Ωより低くなる傾向にあることから、スルーホール周囲のクリアランスを調整します。

3.ACカップリングコンデンサの実装パッド部分が75Ωとなるように調整します。

パッド幅がパターン幅よりも広い場合は、パッド部分で特性インピーダンスが75Ωより低くなるので、実装パッド直下のGND層を抜いて調整します。

シミュレーションでスペック内に収めることで、実機評価時のカット&トライ回数の削減、製品の品質向上や開発期間の短縮などのメリットがございます。